DATASHEET

# GENERAL DESCRIPTION

The AK004-R is a cost optimized sub-1 GHz RF receiver for the 300–348 MHz, 387–464 MHz, and 779–928 MHz frequency bands. The circuit is based on the popular CC1101 RF transceiver, and RF performance characteristics are identical. The AK004-T transmitter together with the AK004-R receiverenable a low-cost RF link.

The RF receiver is integrated with a highly configurable baseband demodulator. The modem supports various modulation formats and has a configurable data rate up to 600 kbps.

The AK004-R provides extensive hardware support for packet handling, data buffering, and burst transmissions.

The main operating parameters and the 64-byte receive FIFO of AK004-R can be controlled through a serial peripheral interface (SPI). In a typical system, the AK004-R will be used together with a microcontroller and a few additional passive components.

# **KEY PRODUCT FEATURES**

### **RF Performance**

Receive Sensitivity Down to -116 dBm at 0.6 kbps Programmable Data Rate from 0.6 to 600 kbps Frequency Bands: 300-348 MHz, 387-464 MHz, and 779-928 MHz

2-FSK, 4-FSK, GFSK, MSK, and OOK Supported **Digital Features**

Flexible Support for Packet Oriented Systems On-chip Support for Sync Word Detection, Flexible Packet Length, and Automatic CRC Calculation

# Low-Power Features

200-nA Sleep Mode Current Consumption Fast Startup Time; 240  $\mu$  s From Sleep to RX Mode 64-Byte RX FIFO

# APPLICATIONS

- Ultra low-power wireless applications operating in the 315/433/868/915 MHz ISM/SRD bands

- Wireless Alarm and Security Systems

- Industrial Monitoring and Control

- Remote Controls

- ♦ Toys

- Home and building automation

| Sub GHz FSK/OOK Receiver Module                                                 | DATASHEET |

|---------------------------------------------------------------------------------|-----------|

| Table of Contents                                                               | Page      |

| 1 Absolute Maximum Ratings                                                      |           |

| 2 Operating Conditions                                                          |           |

| 3 General Characteristics                                                       |           |

| 4 Electrical Specifications                                                     |           |

| 4.1 Current Consumption<br>4.2 RF Receive Section                               |           |

| 4.2 Kr Keelve Section<br>4.3 Crystal Oscillator                                 |           |

| 4.4 Frequency Synthesizer Characteristics                                       |           |

| 4.5 DC Characteristics                                                          |           |

| 4.6 Power-On Reset                                                              |           |

| 5 Pin Configuration                                                             |           |

| 6 Circuit Description                                                           |           |

| 7 Application Circuit                                                           |           |

| 9 Configuration Software                                                        |           |

| 10 4-wire Serial Configuration and Data Interface                               |           |

| 10.1 Chip Status Byte                                                           |           |

| 10.2 Register Access                                                            |           |

| 10.3 SPI Read                                                                   |           |

| 10.4 Command Strobes         11 Microcontroller Interface and Pin Configuration |           |

| 11.1 Configuration Interface                                                    |           |

| 11.2 General Control and Status Pins                                            |           |

| 12 Data Rate Programming                                                        |           |

| 13 Receiver Channel Filter Bandwidth                                            |           |

| 14 Demodulator, Symbol Synchronizer, and Data Decision                          |           |

| 14.1 Frequency Offset Compensation                                              |           |

| 14.2 Bit Synchronization                                                        |           |

| 14.3 Byte Synchronization                                                       |           |

| 15.1 Packet Format                                                              |           |

| 15.1.1 Arbitrary Length Field Configuration                                     |           |

| 15.1.2 Packet Length > 255                                                      |           |

| 15.2 Packet Filtering                                                           |           |

| 15.2.1 Address Filtering                                                        |           |

| 15.2.2 Maximum Length Filtering                                                 |           |

| 15.2.3 CRC Filtering<br>15.3 Packet Handling                                    |           |

| 15.4 Packet Handling in Firmware                                                |           |

| 16 Modulation Formats                                                           |           |

| 16.1 Frequency Shift Keying                                                     |           |

| 16.2 Amplitude Modulation                                                       |           |

| 17 Received Signal Qualifiers and RSSI                                          |           |

| 17.1 Sync Word Qualifier                                                        |           |

| 17.2 RSSI<br>17.3 Carrier Sense (CS)                                            |           |

| 17.3.1 CS Absolute Threshold                                                    |           |

| 17.3.2 CS Relative Threshold                                                    |           |

| 18 Radio Control                                                                |           |

| 18.1 Power-On Start-Up Sequence                                                 |           |

| 18.1.2 Manual Reset.                                                            |           |

| 18.1.1 Automatic POR                                                            |           |

| 18.2 Crystal Control<br>18.3 Voltage Regulator Control                          |           |

| 18.4 Receive Mode (RX)                                                          |           |

| 18.5 RX Termination                                                             |           |

| 18.6 Timing                                                                     |           |

| 18.6.2 Frequency Synthesizer Calibration Time                                   |           |

| 19 RX FIFO                                                                      |           |

| 20 Frequency Programming                                                        |           |

| 21 VCO<br>21.1 VCO and PLL Self-Calibration                                     |           |

| 22 Voltage Regulators                                                           |           |

| 23 General Purpose / Test Output Control Pins                                   |           |

| 24 Asynchronous and Synchronous Serial Operation                                |           |

| 24.1 Asynchronous Serial Operation                                              |           |

# AK004-R

DATASHEET

| 24.2 Synchronous Serial Operation                                                                   | 40 |

|-----------------------------------------------------------------------------------------------------|----|

| 25 System Considerations and Guidelines                                                             | 40 |

| 25.1 SRD Regulations                                                                                | 40 |

| 25.2 Calibration in Multi-Channel Systems                                                           |    |

| 26 Configuration Registers                                                                          | 42 |

| 26.1 Configuration Register Details - Registers with preserved values in SLEEP state 0x00: IOCFG2 - |    |

| Configuration                                                                                       | •  |

| 26.2 Configuration Register Details - Registers that Loose Programming in SLEEP State               | 60 |

| 26.3 Status Register Details                                                                        |    |

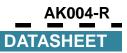

| 27 Module Package OutlineDrawing                                                                    | 64 |

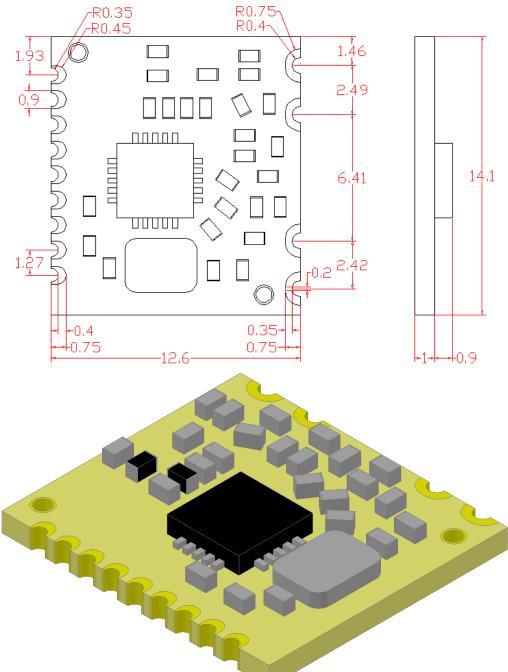

| 28 Recommended PCB Land Pattern                                                                     | 65 |

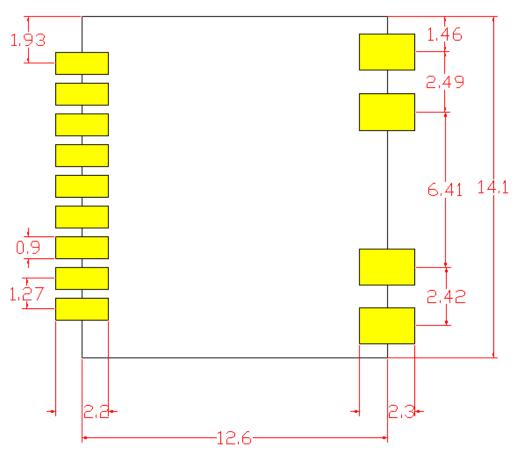

| 29 Tray Packaging                                                                                   | 65 |

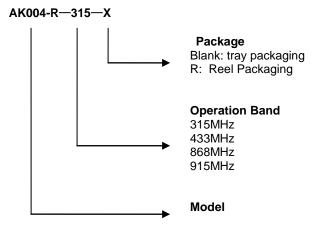

| 30 Ordering Information:                                                                            | 66 |

| 30 Ordering Information:<br>31 Module Revisions:                                                    | 66 |

| 32 Contact us:                                                                                      |    |

- -

# **Index of Figures**

## Page

| 8                                                                                                                           | 0   |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

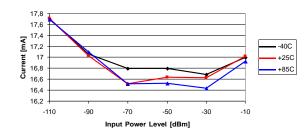

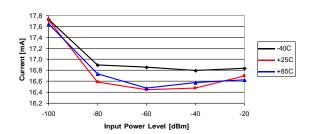

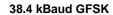

| Figure 1: Typical RX Current Consumption over Temperature and Input Power Level, 868/915 MHz, Sensitivity Optimized Setting |     |

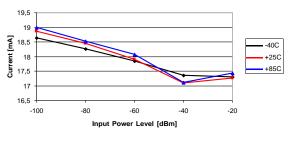

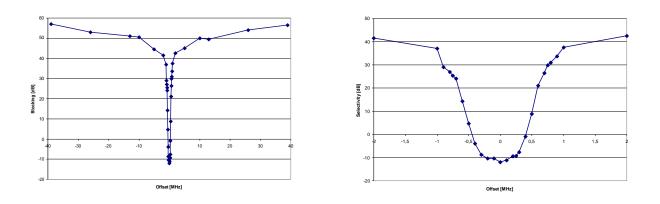

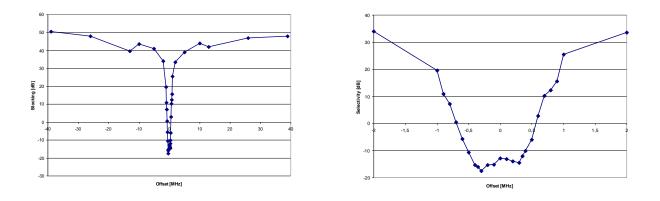

| Figure 2: Typical Selectivity at 1.2 kBaud Data Rate, 868.3 MHz, GFSK, 5.2 kHz Deviation                                    | .10 |

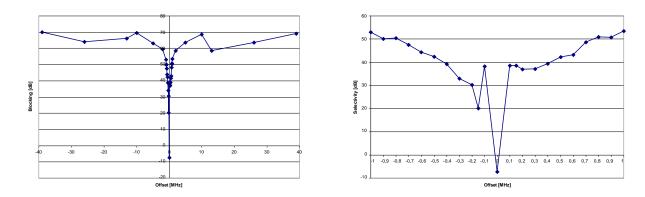

| Figure 3: Typical Selectivity at 38.4 kBaud Data Rate, 868 MHz, GFSK, 20 kHz Deviation.                                     | .11 |

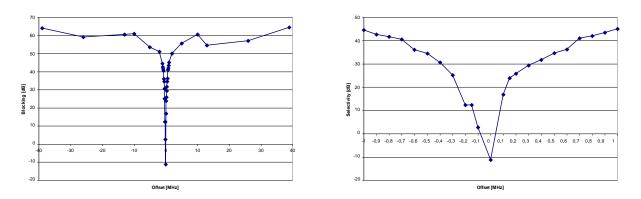

| Figure 4: Typical Selectivity at 250 kBaud Data Rate, 868 MHz, GFSK,                                                        | .11 |

| Figure 5: Typical Selectivity at 500 kBaud Data Rate, 868 MHz, GFSK,                                                        | .11 |

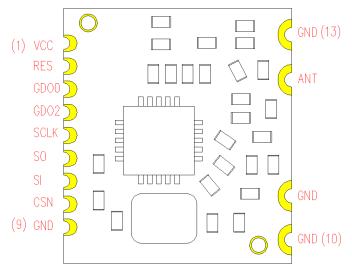

| Figure 6: Pinout Top View                                                                                                   | .13 |

| Figure 7: AK004-R Simplified Block Diagram                                                                                  | .15 |

| Figure 8 Typical Application Schematic                                                                                      | .16 |

| Figure 9: Simplified Radio Control State Diagram, with Typical Current Consumption at                                       |     |

| Figure 10: Configuration Registers Write and Read Operations                                                                | .18 |

| Figure 11: SRES Command Strobe                                                                                              | .21 |

| Figure 12: Register Access Types                                                                                            | .21 |

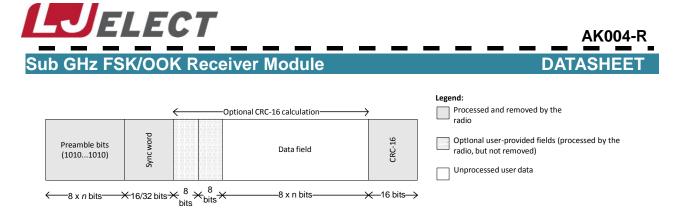

| Figure 13: Packet Format                                                                                                    | .25 |

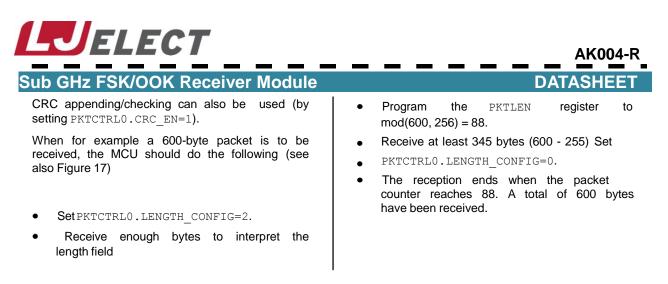

| Figure 14: Packet Length > 255                                                                                              | .26 |

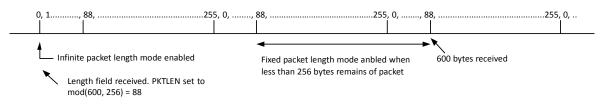

| Figure 15: Data Sent Over the Air (MDMCFG2.MOD_FORMAT=100)                                                                  |     |

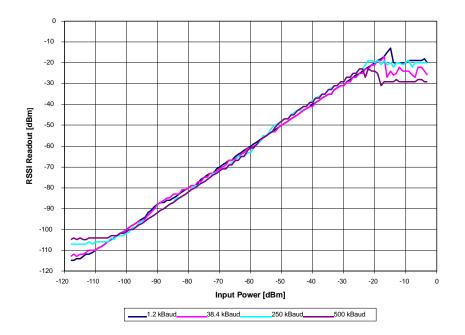

| Figure 16: Typical RSSI Value vs. Input Power Level for Different Data Rates at 433 MHz                                     | .29 |

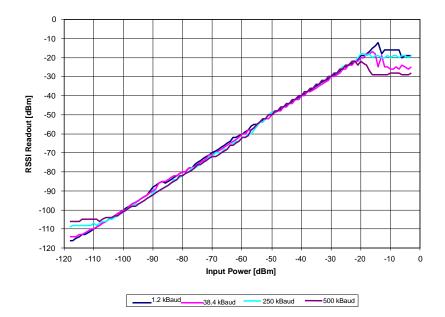

| Figure 17: Typical RSSI Value vs. Input Power Level for Different Data Rates at 868 MHz                                     | .30 |

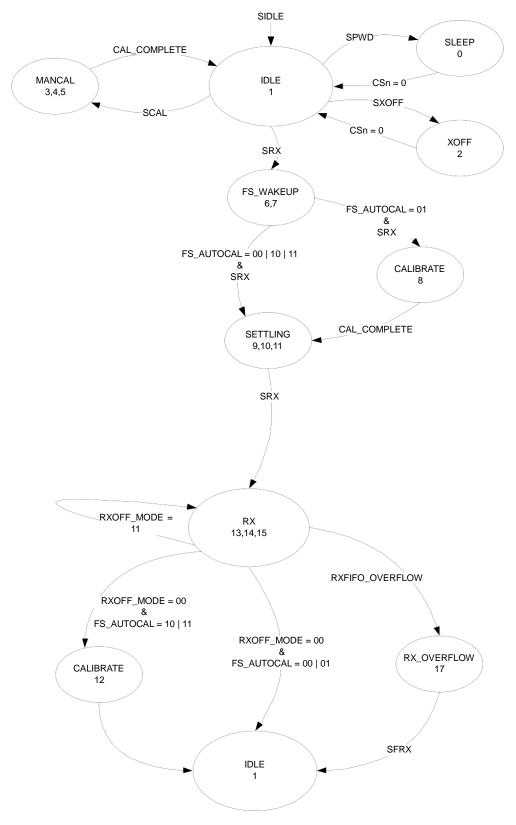

| Figure 18: Complete Radio Control State Diagram                                                                             | .32 |

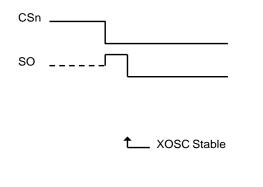

| Figure 19: Power-On Reset with SRES                                                                                         | .33 |

| Figure 20: Power-On Reset                                                                                                   |     |

| Figure 21: Example of RX FIFO at Threshold                                                                                  | .36 |

| Figure 22: Number of Bytes in RX FIFO vs.                                                                                   | .36 |

| the GDO Signal                                                                                                              |     |

| Figure 23. Package Outline Drawing                                                                                          | .65 |

| Index of Tables                                                                                          | Page |

|----------------------------------------------------------------------------------------------------------|------|

| Table 1: Absolute Maximum Ratings                                                                        | 5    |

| Table 1: Absolute Maximum Ratings         Table 2: Operating Conditions                                  | 5    |

| Table 3: General Characteristics                                                                         | 5    |

| Table 3: General Characteristics         Table 4: Current Consumption                                    | 6    |

| Table 5: RF Receive Section                                                                              | 8    |

| Table 6: Typical Sensitivity over Temperature and Supply Voltage, 868 MHz, Sensitivity Optimized Setting | 10   |

| Table 7: Typical Sensitivity over Temperature and Supply Voltage, 915 MHz, Sensitivity Optimized Setting | 10   |

| Table 8: Crystal Oscillator Parameters                                                                   |      |

| Table 9: Frequency Synthesizer Parameters                                                                | 12   |

| Table 10: DC Characteristics                                                                             | 13   |

| Table 11: Power-On Reset Requirements                                                                    | 13   |

| Table 12: Pinout Overview                                                                                | 14   |

| Table 13. BOM of Typical Application                                                                     | 16   |

| Table 14: SPI Interface Timing Requirements                                                              | 19   |

| Table 15: Status Byte Summary                                                                            | 20   |

| Table 16: Data Rate Step Size (assuming a 26 MHz crystal)                                                |      |

| Table 17: Channel Filter Bandwidths [kHz] (assuming a 26 MHz crystal)                                    |      |

| Table 18: Received Packet Status Byte 1 (first byte appended after the data)                             |      |

| Table 19: Received Packet Status Byte 2 (second byte appended after the data)                            | 24   |

# DATASHEET

| Table 20: Symbol Encoding for 2-FSK/GFSK                                                                         |               |

|------------------------------------------------------------------------------------------------------------------|---------------|

| Table 20: Symbol Encoding for 2-FSK/GFSK         Table 21: Sync Word Qualifier Mode                              |               |

| Table 22: Typical RSSI_offset Values                                                                             | 29            |

| Table 23: Typical RSSI Value in dBm at CS Threshold with MAGN_TARGET= 3 (33 dB) at                               |               |

| Table 24: Typical RSSI Value in dBm at CS Threshold with MAGN_TARGET=7 (42 dB) at 250 kBaud, 868 MHz             |               |

| Table 25: Overall State Transition Times (Example for 26 MHz crystal oscillator, 250 kBaud data rate, and TEST0= | 0x0B (maximum |

| calibration time))                                                                                               |               |

| Table 26. Frequency Synthesizer Calibration Times (26/27 MHz crystal)                                            | 35            |

| Table 27: FIFO_THRSettings and the Corresponding RX FIFO Thresholds                                              |               |

| Table 28: GDOx Signal Selection (x = 0, 1, or 2)                                                                 |               |

| Table 29: Command Strobes                                                                                        |               |

| Table 30: Configuration Registers Overview                                                                       | 43            |

| Table 31: Status Registers Overview                                                                              | 44            |

| Table 32: SPI Address Space                                                                                      | 45            |

| Table 33 Revision History                                                                                        | 66            |

# Abbreviations

Abbreviations used in this data sheet are described below.

| 2-FSK | Binary Frequency Shift Keying          | LSB  | Least Significant Bit                |

|-------|----------------------------------------|------|--------------------------------------|

| 4-FSK | Quaternary Frequency Shift Keying      | MCU  | Microcontroller Unit                 |

| ADC   | Analog to Digital Converter            | MSB  | Most Significant Bit                 |

| AFC   | Automatic Frequency Compensation       | N/A  | Not Applicable                       |

| AGC   | Automatic Gain Control                 | NRZ  | Non Return to Zero (Coding)          |

| AMR   | Automatic Meter Reading                | OOK  | On-Off Keying                        |

| BER   | Bit Error Rate                         | PCB  | Printed Circuit Board                |

| ВТ    | Bandwidth-Time product                 | PD   | Power Down                           |

| CFR   | Code of Federal Regulations            | PER  | Packet Error Rate                    |

| CRC   | Cyclic Redundancy Check                | PLL  | Phase Locked Loop                    |

| CS    | Carrier Sense                          | POR  | Power-On Reset                       |

| DC    | Direct Current                         | PTAT | Proportional To Absolute Temperature |

| DVGA  | Digital Variable Gain Amplifier        | QLP  | Quad Leadless Package                |

| ESR   | Equivalent Series Resistance           | QPSK | Quadrature Phase Shift Keying        |

| FCC   | Federal Communications Commission      | RC   | Resistor-Capacitor                   |

| FIFO  | First-In-First-Out                     | RF   | Radio Frequency                      |

| FS    | Frequency Synthesizer                  | RSSI | Received Signal Strength Indicator   |

| GFSK  | Gaussian shaped Frequency Shift Keying | RX   | Receive, Receive Mode                |

| IF    | Intermediate Frequency                 | SMD  | Surface Mount Device                 |

| I/Q   | In-Phase/Quadrature                    | SPI  | Serial Peripheral Interface          |

| ISM   | Industrial, Scientific, Medical        | SRD  | Short Range Devices                  |

| LC    | Inductor-Capacitor                     | VCO  | Voltage Controlled Oscillator        |

| LNA   | Low Noise Amplifier                    | XOSC | Crystal Oscillator                   |

| LO    |                                        |      |                                      |

# DATASHEET

# Sub GHz FSK/OOK Receiver Module

# 1 Absolute Maximum Ratings

Under no circumstances must the absolute maximum ratings given in Table 1 be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

## **Table 1: Absolute Maximum Ratings**

| Parameter                                     | Min  | Max                      | Units | Condition                                                         |

|-----------------------------------------------|------|--------------------------|-------|-------------------------------------------------------------------|

| Supply voltage                                | -0.3 | 3.9                      | V     | All supply pins must have the same voltage                        |

| Voltage on any digital pin                    | -0.3 | VDD +<br>0.3,<br>max 3.9 | V     |                                                                   |

| Voltage on the pins RF_P, RF_N, DCOUPL, RBIAS | -0.3 | 2.0                      | V     |                                                                   |

| Voltage ramp-up rate                          |      | 120                      | kV/µs |                                                                   |

| Input RF level                                |      | +10                      | dBm   |                                                                   |

| Storage temperature range                     | -50  | 150                      | °C    |                                                                   |

| Solder reflow temperature                     |      | 260                      | °C    | According to IPC/JEDEC J-STD-020                                  |

| ESD                                           |      | 750                      | V     | According to JEDEC STD 22, method A114, Human<br>Body Model (HBM) |

| ESD                                           |      | 400                      | V     | According to JEDEC STD 22, C101C, Charged<br>Device Model (CDM)   |

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

# **2 Operating Conditions**

The operating conditions for **AKOO4-R** are listed in Table 2 below.

# **Table 2: Operating Conditions**

| Parameter                | Min | Max | Unit | Condition                                  |

|--------------------------|-----|-----|------|--------------------------------------------|

| Operating temperature    | -40 | 85  | °C   |                                            |

| Operating supply voltage | 1.8 | 3.6 | V    | All supply pins must have the same voltage |

# **3 General Characteristics**

# **Table 3: General Characteristics**

| Parameter       | Min | Max | Unit  | Condition/Note                                                                |

|-----------------|-----|-----|-------|-------------------------------------------------------------------------------|

| Frequency range | 300 | 348 | MHz   |                                                                               |

|                 | 387 | 464 | MHz   | If using a 27 MHz crystal, the lower frequency limit for this band is 392 MHz |

|                 | 779 | 928 | MHz   |                                                                               |

|                 | 0.6 | 500 | kBaud | 2-FSK                                                                         |

|                 | 0.6 | 250 | kBaud | GFSK and OOK                                                                  |

| Data rate       |     |     | kBaud | 4-FSK (the data rate in kbps will be twice the baud rate)                     |

|                 | 0.6 | 300 |       | Optional Manchester encoding (the data rate in kbps will the baud rate)       |

# **4 Electrical Specifications**

# **4.1 Current Consumption**

$T_A = 25 \ ^{\circ}C$ , VDD = 3.0 V if nothing else stated. All measurement results are obtained using [1] and [2]. Reduced current settings (MDMCFG2.DEM\_DCFILT\_OFF=1) gives a slightly lower current consumption at the cost of a reduction in sensitivity. See Table 5 for additional details on current consumption and sensitivity.

# Table 4: Current Consumption

| Parameter                          | Min | Тур  | Max | Unit | Condition                                                                                                                |

|------------------------------------|-----|------|-----|------|--------------------------------------------------------------------------------------------------------------------------|

| Current<br>onsumption in           |     | 0.2  | 1   | μA   | Voltage regulator to digital part off, register values retained (SLEEP state). All GDO pins programmed to 0x2F (HW to 0) |

| power down<br>modes                |     | 100  |     | μA   | Voltage regulator to digital part off, register values retained,<br>XOSC running (SLEEP state with MCSM0.OSC_FORCE_ON    |

|                                    |     | 165  |     | μA   | Voltage regulator to digital part on, all other modules in power down (XOFF state)                                       |

| Current consumption                |     | 1.7  |     | mA   | Only voltage regulator to digital part and crystal oscillator running (IDLE state)                                       |

|                                    |     | 8.4  |     | mA   | The current consumption for the intermediate states when going from IDLE to RX, including the calibration state          |

| Current<br>consumption,<br>315 MHz |     | 15.4 |     | mA   | Receive mode, 1.2 kBaud, reduced current, input at sensitivity<br>limit                                                  |

|                                    |     | 14.4 |     | mA   | Receive mode, 1.2 kBaud, register settings optimized for reduced current, input well above sensitivity limit             |

|                                    |     | 15.2 |     | mA   | Receive mode, 38.4 kBaud, register settings optimized for reduced current, input at sensitivity limit                    |

|                                    |     | 14.3 |     | mA   | Receive mode, 38.4 kBaud, register settings optimized for reduced current, input well above sensitivity limit            |

|                                    |     | 16.5 |     | mA   | Receive mode, 250 kBaud, register settings optimized for<br>reduced current, input at sensitivity limit                  |

|                                    |     | 15.1 |     | mA   | Receive mode, 250 kBaud, register settings optimized for reduced current, input well above sensitivity limit             |

| Current consumption,               |     | 16.0 |     | mA   | Receive mode, 1.2 kBaud, register settings optimized for reduced current, input at sensitivity limit                     |

| 433 MHz                            |     | 15.0 |     | mA   | Receive mode, 1.2 kBaud, register settings optimized for reduced current, input well above sensitivity limit             |

|                                    |     | 15.7 |     | mA   | Receive mode, 38.4 kBaud, register settings optimized for reduced current, input at sensitivity limit                    |

|                                    |     | 15.0 |     | mA   | Receive mode, 38.4 kBaud, register settings optimized for reduced current, input well above sensitivity limit            |

|                                    |     | 17.1 |     | mA   | Receive mode, 250 kBaud, register settings optimized for reduced current, input at sensitivity limit                     |

|                                    |     | 15.7 |     | mA   | Receive mode, 250 kBaud, register settings optimized for reduced current, input well above sensitivity limit             |

| Parameter                              | Min | Тур  | Ма | Uni | Condition                                                                                                                                                                                            |

|----------------------------------------|-----|------|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current<br>consumption,<br>868/915 MHz |     | 15.7 |    | mA  | Receive mode, 1.2 kBaud, register settings optimized for reduced current, input at sensitivity limit. See Figure 1 for current consumption with register settings optimized for sensitivity.         |

|                                        |     | 14.7 |    | mA  | Receive mode, 1.2 kBaud, register settings optimized for reduced current, input well above sensitivity limit. See Figure 1 for current consumption with register settings optimized for sensitivity. |

|                                        |     | 15.6 |    | mA  | Receive mode, 38.4 kBaud, register settings optimized for reduced current, input at sensitivity limit. See Figure 1 for current consumption with register settings optimized for sensitivity.        |

|                                        |     | 14.6 |    | mA  | Receive mode, 38.4 kBaud, register settings optimized for<br>reduced current, input well above sensitivity limit. See Figure 1<br>for current consumption with register settings optimized for       |

|                                        |     | 16.9 |    | mA  | Receive mode, 250 kBaud, register settings optimized for reduced current, input at sensitivity limit. See Figure 1 for current consumption with register settings optimized for sensitivity.         |

|                                        |     | 15.6 |    | mA  | Receive mode, 250 kBaud, register settings optimized for reduced current, input well above sensitivity limit. See Figure 1 for current consumption with register settings optimized for sensitivity. |

250 kBaud GFSK

Figure 1: Typical RX Current Consumption over Temperature and Input Power Level, 868/915 MHz, Sensitivity Optimized Setting

AK004-R

DATASH

# 4.2 RF Receive Section

$T_{\text{A}}$  = 25  $\,^\circ\!\mathrm{C}$  , VDD = 3.0 V if nothing else stated. All measurement results are obtained using [1] and [2].

## Table 5: RF Receive Section

| Parameter                                                                                                                                                                                        | Min                          | Тур                                | Max                         | Unit                       | Condition/Note                                                                                                                                                                                                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------|-----------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Digital channel<br>filter bandwidth                                                                                                                                                              | 58                           |                                    | 812                         | kHz                        | User programmable. The bandwidth limits are proportional to crystal frequency (given values assume a 26.0 MHz crystal)                                                                                                                                   |  |

| Spurious<br>emissions                                                                                                                                                                            |                              | -68                                | -57                         | dBm                        | 25 MHz - 1 GHz<br>(Maximum figure is the ETSI EN 300 220 V2.3.1 limit)                                                                                                                                                                                   |  |

|                                                                                                                                                                                                  |                              | -66                                | -47                         | dBm                        | Above 1 GHz<br>(Maximum figure is the ETSI EN 300 220 V2.3.1 limit)                                                                                                                                                                                      |  |

|                                                                                                                                                                                                  |                              |                                    |                             |                            | Typical radiated spurious emission is -49 dBm measured at the VCO frequency                                                                                                                                                                              |  |

| RX latency                                                                                                                                                                                       |                              | 9                                  |                             | bit                        | Serial operation. Time from start of reception until data is available on the receiver data output pin is equal to 9 bit                                                                                                                                 |  |

| 315 MHz                                                                                                                                                                                          |                              |                                    |                             |                            |                                                                                                                                                                                                                                                          |  |

| <b>1.2 kBaud data r</b><br>(2-FSK, 1% packe                                                                                                                                                      | a <b>te, sei</b><br>et error | n <b>sitivity o</b><br>rate, 20 b  | <b>ptimize</b><br>ytes pac  | ed, MDMC<br>cket leng      | <b>CFG2.DEM_DCFILT_OFF=0</b><br>th, 5.2 kHz deviation, 58 kHz digital channel filter bandwidth)                                                                                                                                                          |  |

| Receiver<br>sensitivity                                                                                                                                                                          |                              | -111                               |                             | dBm                        | Sensitivity can be traded for current consumption by setting MDMCFG2.DEM_DCFILT_OFF=1. The typical current consumption is then reduced from 17.2 mA to 15.4 mA at the sensitivity limit. The sensitivity is typically reduced to -109 dBm                |  |

| 433 MHz                                                                                                                                                                                          |                              |                                    |                             |                            |                                                                                                                                                                                                                                                          |  |

| <b>0.6 kBaud data rate, sensitivity optimized, MDMCFG2.DEM_DCFILT_OFF=0</b><br>(GFSK, 1% packet error rate, 20 bytes packet length, 14.3 kHz deviation, 58 kHz digital channel filter bandwidth) |                              |                                    |                             |                            |                                                                                                                                                                                                                                                          |  |

| Receiver sensitivity                                                                                                                                                                             |                              | -116                               |                             | dBm                        |                                                                                                                                                                                                                                                          |  |

| <b>1.2 kBaud data r</b><br>(GFSK, 1% packe                                                                                                                                                       | ate, ser<br>et error         | n <b>sitivity o</b><br>rate, 20 by | p <b>timize</b><br>/tes pac | ed, MDMC<br>ket leng       | <b>CFG2.DEM_DCFILT_OFF=0</b><br>th, 5.2 kHZ deviation, 58 kHz digital channel filter bandwidth)                                                                                                                                                          |  |

| Receiver<br>sensitivity                                                                                                                                                                          |                              | -112                               |                             | dBm                        | Sensitivity can be traded for current consumption by setting $MDMCFG2.DEM\_DCFILT\_OFF=1$ . The typical current consumption is then reduced from 18.0 mA to 16.0 mA at the sensitivity limit. The sensitivity is typically reduced to $-110 \text{ dBm}$ |  |

| <b>38.4 kBaud data</b><br>(GFSK, 1% packe                                                                                                                                                        | rate, se<br>et error         | ensitivity<br>rate, 20 by          | <b>optimiz</b><br>/tes pac  | <b>ed, MDN</b><br>ket leng | ICFG2.DEM DCFILT OFF=0<br>th, 20 kHz deviation, 100 kHz digital channel filter bandwidth)                                                                                                                                                                |  |

| Receiver sensitivity                                                                                                                                                                             |                              | -104                               |                             | dBm                        |                                                                                                                                                                                                                                                          |  |

| 250 kBaud data<br>(GFSK, 1% packe                                                                                                                                                                | rate, se<br>et error         | nsitivity o<br>rate, 20 by         | o <b>ptimiz</b><br>/tes pac | <b>ed, мом</b><br>ket leng | CFG2.DEM_DCFILT_OFF=0<br>th, 127 kHz deviation, 540 kHz digital channel filter bandwidth)                                                                                                                                                                |  |

| Receiver<br>sensitivity                                                                                                                                                                          |                              | -95                                |                             | dBm                        |                                                                                                                                                                                                                                                          |  |

| Parameter                                                    | Min                           | Тур                            | Max                  | Unit                              | Condition/Note                                                                                                                                                                                                                 |

|--------------------------------------------------------------|-------------------------------|--------------------------------|----------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 868/915 MHz                                                  |                               |                                |                      |                                   |                                                                                                                                                                                                                                |

| <b>1.2 kBaud data rate, sen</b> (GFSK, 1% packet error ra    | <b>sitivity</b><br>ate, 20    | <b>optimize</b><br>bytes pac   | ed, MDM<br>cket leng | <b>c<b>FG2</b>.1<br/>gth, 5.2</b> | DEM_DCFILT_OFF=0<br>kHz deviation, 58 kHz digital channel filter bandwidth)                                                                                                                                                    |

| Receiver sensitivity                                         |                               | -112                           |                      | dBm                               | Sensitivity can be traded for current consumption by setting MDMCFG2.DEM_DCFILT_OFF=1. The typical current consumption is then reduced from 17.7 mA to 15.7 mA at sensitivity limit. The sensitivity is typically reduced to   |

| Saturation                                                   |                               | -14                            |                      | dBm                               | FIFOTHR.CLOSE_IN_RX=0. See more in DN010 [5]                                                                                                                                                                                   |

| Adjacent channel<br>rejection<br>±100 kHz offset             |                               | 37                             |                      | dB                                | Desired channel 3 dB above the sensitivity<br>limit. 100 kHz channel spacing<br>See Figure 2 for selectivity performance at other offset<br>frequencies                                                                        |

| Image channel rejection                                      |                               | 31                             |                      | dB                                | IF frequency 152 kHz                                                                                                                                                                                                           |

| Image channel rejection                                      |                               | 51                             |                      | uВ                                | Desired channel 3 dB above the sensitivity limit                                                                                                                                                                               |

| Blocking<br>±2 MHz offset<br>±10 MHz offset                  |                               | -50<br>-40                     |                      | dBm<br>dBm                        | Desired channel 3 dB above the sensitivity limit<br>See Figure 2 for blocking performance at other offset<br>frequencies                                                                                                       |

| <b>38.4 kBaud data rate, se</b><br>(GFSK, 1% packet error ra | <b>nsitivit</b><br>ate, 20    | <b>y optimi</b> z<br>bytes pao | zed, MD              | <b>мсғс2</b><br>gth, 20           | DEM_DCFILT_OFF=0<br>kHz deviation, 100 kHz digital channel filter bandwidth)                                                                                                                                                   |

| Receiver sensitivity                                         |                               | -104                           |                      | dBm                               | Sensitivity can be traded for current consumption by setting MDMCFG2.DEM_DCFILT_OFF=1. The typical current consumption is then reduced from 17.7 mA to 15.6 mA at the sensitivity limit. The sensitivity is typically          |

| Saturation                                                   |                               | -16                            |                      | dBm                               | FIFOTHR.CLOSE_IN_RX=0. See more in DN010 [5]                                                                                                                                                                                   |

| Adjacent channel<br>200 kHz offset<br>+200 kHz offset        |                               | 12<br>25                       |                      | dB<br>dB                          | Desired channel 3 dB above the sensitivity limit.<br>200 kHz channel spacing<br>See Figure 3 for blocking performance at other offset<br>frequencies                                                                           |

| Image channel rejection                                      |                               | 23                             |                      | dB                                | IF frequency 152 kHz<br>Desired channel 3 dB above the sensitivity limit                                                                                                                                                       |

| Blocking<br>±2 MHz offset<br>±10 MHz offset                  |                               | -50<br>-40                     |                      | dBm<br>dBm                        | Desired channel 3 dB above the sensitivity limit<br>See Figure 3 for blocking performance at other offset<br>frequencies                                                                                                       |

| <b>250 kBaud data rate, ser</b><br>(GFSK, 1% packet error ra | n <b>sitivit</b> y<br>ate, 20 | <b>y optimiz</b><br>bytes pao  | ed, MDN<br>cket leng | <b>ICFG2</b> .<br>gth, 127        | DEM_DCFILT_OFF=0<br>7 kHz deviation, 540 kHz digital channel filter bandwidth)                                                                                                                                                 |

| Receiver sensitivity                                         |                               | -95                            |                      | dBm                               | Sensitivity can be traded for current consumption by<br>setting MDMCFG2.DEM_DCFILT_OFF=1. The typical<br>current consumption is then reduced from 18.9 mA to 16.9<br>mA at the sensitivity limit. The sensitivity is typically |

| Saturation                                                   |                               | -17                            |                      | dBm                               | FIFOTHR.CLOSE_IN_RX=0. See more in DN010 [5]                                                                                                                                                                                   |

| Adjacent channel<br>rejection                                |                               | 25                             |                      | dB                                | Desired channel 3 dB above the sensitivity<br>limit. 750 kHz channel spacing<br>See Figure 4 for blocking performance at other offset<br>frequencies                                                                           |

| Image channel rejection                                      |                               | 14                             |                      | dB                                | IF frequency 304 kHz<br>Desired channel 3 dB above the sensitivity limit                                                                                                                                                       |

| Blocking<br>±2 MHz offset<br>±10 MHz offset                  |                               | -50<br>-40                     |                      | dBm<br>dBm                        | Desired channel 3 dB above the sensitivity limit<br>See Figure 4 for blocking performance at other offset<br>frequencies                                                                                                       |

AK004-R DATASHEET

| Parameter                                                                                                                                                                                                    | Min                          | Тур                          | Max                        | Unit                          | Condition/Note                                                                              |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|----------------------------|-------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| <b>4-FSK, 125 kBaud data rate (250 kbps), sensitivity optimized, MDMCFG2.DEM_DCFILT_OFF=0</b><br>(1% packet error rate, 20 bytes packet length, 127 kHz deviation, 406 kHz digital channel filter bandwidth) |                              |                              |                            |                               |                                                                                             |  |  |  |  |

| Receiver sensitivity                                                                                                                                                                                         |                              | -96                          |                            | dBm                           |                                                                                             |  |  |  |  |

| <b>4-FSK, 250 kBaud data</b> (1% packet error rate, 20                                                                                                                                                       | <b>rate (500</b><br>bytes pa | <b>kbps), s</b><br>cket leng | <b>sensitiv</b><br>th, 254 | <b>/ity optin</b><br>kHz devi | nized, MDMCFG2.DEM_DCFILT_OFF=0<br>ation, 812 kHz digital channel filter bandwidth          |  |  |  |  |

| Receiver sensitivity                                                                                                                                                                                         |                              | -91                          |                            | dBm                           |                                                                                             |  |  |  |  |

| (1% packet error rate, 20                                                                                                                                                                                    | <b>rate (600</b><br>bytes pa | cket leng                    | s <b>ensitiv</b><br>h, 228 | kHz devi                      | <b>nized, MDMCFG2</b> .DEM_DCFILT_OFF=0<br>ation, 812 kHz digital channel filter bandwidth) |  |  |  |  |

| Receiver sensitivity                                                                                                                                                                                         |                              | -89                          |                            | dBm                           |                                                                                             |  |  |  |  |

Table 6: Typical Sensitivity over Temperature and Supply Voltage, 868 MHz, Sensitivity Optimized

Setting

|                              | Supply Voltage<br>VDD = 1.8 V |      |      | Supply<br>Voltage VDD |      |      | Supply Voltage<br>VDD = 3.6 V |      |      |

|------------------------------|-------------------------------|------|------|-----------------------|------|------|-------------------------------|------|------|

| Temperature [°C]             | -40                           | 25   | 85   | -40                   | 25   | 85   | -40                           | 25   | 85   |

| Sensitivity [dBm] 1.2 kBaud  | -113                          | -112 | -110 | -113                  | -112 | -110 | -113                          | -112 | -110 |

| Sensitivity [dBm] 38.4 kBaud | -105                          | -104 | -102 | -105                  | -104 | -102 | -105                          | -104 | -102 |

| Sensitivity [dBm] 250 kBaud  | -97                           | -96  | -92  | -97                   | -95  | -92  | -97                           | -94  | -92  |

| Sensitivity [dBm] 500 kBaud  | -91                           | -90  | -86  | -91                   | -90  | -86  | -91                           | -90  | -86  |

Table 7: Typical Sensitivity over Temperature and Supply Voltage, 915 MHz, Sensitivity Optimized Setting

|                              | Supply<br>Voltage |      |      | Supply<br>VDD = 3 | Voltag<br>3.0 V | e    | Supply Voltage<br>VDD = 3.6 V |      |      |

|------------------------------|-------------------|------|------|-------------------|-----------------|------|-------------------------------|------|------|

| Temperature [°C]             | -40               | 25   | 85   | -40               | 25              | 85   | -40                           | 25   | 85   |

| Sensitivity [dBm] 1.2 kBaud  | -113              | -112 | -110 | -113              | -112            | -110 | -113                          | -112 | -110 |

| Sensitivity [dBm] 38.4 kBaud | -105              | -104 | -102 | -104              | -104            | -102 | -105                          | -104 | -102 |

| Sensitivity [dBm] 250 kBaud  | -97               | -94  | -92  | -97               | -95             | -92  | -97                           | -95  | -92  |

| Sensitivity [dBm] 500 kBaud  | -91               | -89  | -86  | -91               | -90             | -86  | -91                           | -89  | -86  |

Figure 2: Typical Selectivity at 1.2 kBaud Data Rate, 868.3 MHz, GFSK, 5.2 kHz Deviation. IF Frequency is 152.3 kHz and the Digital Channel Filter Bandwidth is 58 kHz

*Figure 3: Typical Selectivity at 38.4 kBaud Data Rate, 868 MHz, GFSK, 20 kHz Deviation.* **IF Frequency is 152.3 kHz and the Digital Channel Filter Bandwidth is 100 kHz**

*Figure 4: Typical Selectivity at 250 kBaud Data Rate, 868 MHz, GFSK,* **IF Frequency is 304 kHz and the Digital Channel Filter Bandwidth is 540 kHz**

Figure 5: Typical Selectivity at 500 kBaud Data Rate, 868 MHz, GFSK, IF Frequency is 355 kHz and the Digital Channel Filter Bandwidth is 812 kHz

AK004-R

DATA

# 4.3 Crystal Oscillator

$T_A$  = 25 °C, VDD = 3.0 V if nothing else is stated. All measurement results obtained using [1] and [2].

| Parameter                | Min | Тур | Max | Unit | Condition/Note                                                                                                                                                                                                                                 |

|--------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal<br>frequenc<br>y | 26  | 26  | 27  | MHz  | For compliance with modulation bandwidth requirements under EN 300 220 V2.3.1 in the 863 to 870 MHz frequency range it is recommended to use a 26 MHz crystal for frequencies below 869 MHz and a 27 MHz crystal for frequencies above 869 MHz |

| Tolerance                |     | ±40 |     | ppm  | This is the total tolerance including a) initial tolerance, b) crystal loading, c) aging, and d) temperature dependence. The acceptable crystal tolerance depends on RF frequency and                                                          |

| Load<br>capacitanc       | 10  | 13  | 20  | pF   | Simulated over operating conditions                                                                                                                                                                                                            |

| ESR                      |     |     | 100 | Ω    |                                                                                                                                                                                                                                                |

| Start-up time            |     | 150 |     | μs   | This parameter is to a large degree crystal dependent. Measured on [1] and [2] using crystal AT-41CD2 from NDK                                                                                                                                 |

# **Table 8: Crystal Oscillator Parameters**

# 4.4 Frequency Synthesizer Characteristics

$T_A = 25 \ ^{\circ}C$ , VDD = 3.0 V if nothing else is stated. All measurement results are obtained using [1] and [2]. Min figures are given using a 27 MHz crystal. Typ. and max figures are given using a 26 MHz crystal

| Parameter                              | Min | Тур       | Max | Unit   | Condition/Note                                                                                                                       |  |  |  |  |

|----------------------------------------|-----|-----------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Programmed<br>frequency resolution     | 397 | Fxosc/216 | 412 | Hz     | 26 - 27 MHz crystal. The resolution (in Hz) is equal for all frequency bands                                                         |  |  |  |  |

| Synthesizer<br>frequency tolerance     |     | ±40       |     | ppm    | Given by crystal used. Required accuracy (including temperature and aging) depends on frequency band and channel bandwidth / spacing |  |  |  |  |

| RF carrier phase noise                 |     | -92       |     | dBc/Hz | @ 50 kHz offset from carrier                                                                                                         |  |  |  |  |

| RF carrier phase noise                 |     | -92       |     | dBc/Hz | @ 100 kHz offset from carrier                                                                                                        |  |  |  |  |

| RF carrier phase noise                 |     | -92       |     | dBc/Hz | @ 200 kHz offset from carrier                                                                                                        |  |  |  |  |

| RF carrier phase noise                 |     | -98       |     | dBc/Hz | @ 500 kHz offset from carrier                                                                                                        |  |  |  |  |

| RF carrier phase noise                 |     | -107      |     | dBc/Hz | @ 1 MHz offset from carrier                                                                                                          |  |  |  |  |

| RF carrier phase noise                 |     | -113      |     | dBc/Hz | @ 2 MHz offset from carrier                                                                                                          |  |  |  |  |

| RF carrier phase noise                 |     | -119      |     | dBc/Hz | @ 5 MHz offset from carrier                                                                                                          |  |  |  |  |

| RF carrier phase noise                 |     | -129      |     | dBc/Hz | @ 10 MHz offset from carrier                                                                                                         |  |  |  |  |

| PLL turn-on<br>time ( See<br>Table 26) | 72  | 75        | 75  | μs     | Time from leaving the IDLE state until arriving in the RX state, when not performing calibration. Crystal oscillator running.        |  |  |  |  |

| PLL calibration time<br>(See Table 27) | 685 | 712       | 724 | μs     | Calibration can be initiated manually or automatically before entering or after leaving RX                                           |  |  |  |  |

# 4.5 DC Characteristics

$T_A = 25 C$  if nothing else stated.

### Table 10: DC Characteristics

| Digital Inputs/Outputs   | Min                   | Мах | Uni | Condition                     |

|--------------------------|-----------------------|-----|-----|-------------------------------|

| Logic "0" input voltage  | 0                     | 0.7 | V   |                               |

| Logic "1" input voltage  | voltage VDD – 0.7 VDE |     | V   |                               |

| Logic "0" output voltage | 0 0.5                 |     | V   | For up to 4 mA output current |

| Logic "1" output voltage | oltage VDD – 0.3 VDD  |     | V   | For up to 4 mA output current |

| Logic "0" input current  | put current N/A –50   |     | n   | Input equals 0 V              |

| Logic "1" input current  | current N/A 50        |     | n   | Input equals VDD              |

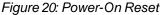

### 4.6 Power-On Reset

For proper Power-On-Reset functionality the power supply should comply with the requirements in Table 11 below. Otherwise, the chip should be assumed to have unknown state until transmitting an SRES strobe over the SPI interface. See Section 18.1 on page 36 for further details.

#### **Table 11: Power-On Reset Requirements**

| Parameter             | Min | Тур | Мах | Unit | Condition/Note                              |

|-----------------------|-----|-----|-----|------|---------------------------------------------|

| Power-up ramp-up time |     |     | 5   | ms   | From 0V until reaching 1.8V                 |

| Power off time        | 1   |     |     | ms   | Minimum time between power-on and power-off |

# **5** Pin Configuration

The **AKOO4-R** pin-out is shown in Figure 6 and Table 12. See Section 23 for details on the I/O configuration.

#### Figure 6: Pinout Top View

**Note:** The exposed die attach pad **must** be connected to a solid ground plane as this is the main ground connection for the chip

# Table 12: Pinout Overview

| Pin #      | Pin Name | Pin type       | Description                                                                                                                                         |

|------------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VCC      | Power supply+  | 1.8-3.6V power supply for module                                                                                                                    |

| 2          | RES      | Digital Input  | Reset trigger input.                                                                                                                                |

| 3          | GDO0     | Digital Output | Digital output pin for general use:<br>• Test signals<br>• FIFO status signals<br>• Clock output, down-divided from XOSC<br>• Serial output RX data |

| 4          | GDO02    | Digital Output | Digital output pin for general use:<br>• Test signals<br>• FIFO status signals<br>• Clock output, down-divided from XOSC<br>• Serial output RX data |

| 5          | SCLK     | Digital Input  | Serial configuration interface, clock input                                                                                                         |

| 6          | SO       | Digital Output | Serial configuration interface, data output<br>Optional general output pin when CSn is high                                                         |

| 7          | SI       | Digital Input  | SPI Data input.                                                                                                                                     |

| 8          | SCN      | Digital Input  | Serial configuration interface, chip select.                                                                                                        |

| 9,10,11,13 | GND      | Ground         | Module ground.                                                                                                                                      |

| 12         | ANT      | Digital Input  | Module Antenna terminal, Default terminal                                                                                                           |

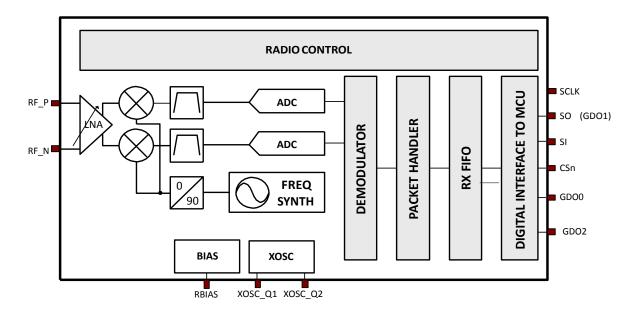

**6 Circuit Description**

# Figure 7: AK004-R Simplified Block Diagram

A simplified block diagram of **AKOD4-R** is shown in Figure 7.

**AKOD4-R** features a low-IF receiver. The received RF signal is amplified by the low-noise amplifier (LNA) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). At IF, the I/Q signals are digitised by the ADCs. Automatic gain control (AGC), fine channel filtering, demodulation, and bit/packet synchronization are performed digitally.

The frequency synthesizer includes a completely on-chip LC VCO and a 90 degree phase shifter for generating the I and Q LO signals to the down-conversion mixers in receive mode.

A crystal is to be connected to XOSC\_Q1 and XOSC\_Q2. The crystal oscillator generates the reference frequency for the synthesizer, as well as clocks for the ADC and the digital part.

A 4-wire SPI serial interface is used for configuration and data buffer access.

The digital baseband includes support for channel configuration, packet handling, and data buffering.

C5

C6

C7

C8

CAP CER 10uF/16V 20% X5R 0402 RoHS

CAP CER 0.1uF/25V 20% X7R 0402 RoHS

CAP CER 47uF/16V 20% X5R 1206 RoHS

CAP CER 0.1uF/25V 20% X7R 0402 RoHS

Web: www.ljelect.com

MURATA

MURATA

MURATA

MURATA

| Table 13. BOM of Typical Application |                                          |                |  |  |  |  |  |  |  |  |

|--------------------------------------|------------------------------------------|----------------|--|--|--|--|--|--|--|--|

| Designator                           | Descriptions                             | Manufacturer   |  |  |  |  |  |  |  |  |

| M1                                   | Module AK004-R 12.6*14.1*1.9mm RoHS      | LJ ELECTRONICS |  |  |  |  |  |  |  |  |

| U1                                   | IC 8 BIT MCU STM8S003F3 SSOP20 RoHS      | MICROICHIP     |  |  |  |  |  |  |  |  |

| U2                                   | IC LDO XC6206P33PR 3.3V SOT-23 RoHS      | TOREX          |  |  |  |  |  |  |  |  |

| L1                                   | Thick film resistor0R 5% 1/16W 0402 RoHS | ROHM           |  |  |  |  |  |  |  |  |

| C1                                   | CAP CER 0402 DO NOT FIT                  |                |  |  |  |  |  |  |  |  |

| C2                                   | CAP CER 0402 DO NOT FIT                  |                |  |  |  |  |  |  |  |  |

| C3                                   | CAP CER 0.1uF/25V 20% X7R 0402 RoHS      | MURATA         |  |  |  |  |  |  |  |  |

| C4                                   | CAP CER 0.1uF/25V 20% X7R 0402 RoHS      | MURATA         |  |  |  |  |  |  |  |  |

|                          |                                                      | C5<br>10uF<br>C3<br>0. 1ul |                                                              |               |                          | 7<br>7uF |  |

|--------------------------|------------------------------------------------------|----------------------------|--------------------------------------------------------------|---------------|--------------------------|----------|--|

| U1<br>MCU<br>VACP<br>GND | VDD<br>PD1<br>PD2<br>PD3<br>PD4<br>PD5<br>PD6<br>PD7 |                            | VCC<br>RES<br>GDOO<br>GDO2<br>SCLK<br>SO<br>SI<br>CSN<br>GND | M1<br>AK004-R | GND<br>ANT<br>GND<br>GND |          |  |

Figure 8 Typical Application Schematic

3. 3V

U2

IN

OUT LDP

# **7** Application Circuit

Sub GHz FSK/OOK Receiver Module

DATASHEET

4. 5V

VBAT

AK004-R

# 8 Configuration Overview

**AKO04-R** can be configured to achieve optimum performance for many different applications. Configuration is done using the SPI interface. See Section 10 for more description of the SPI interface. The following key parameters can be programmed:

- Power-down / power up mode

- Crystal oscillator power-up / power-down

- Receive mode

- Carrier Frequency / RF channel Data

- rate

- Modulation format

- RX channel filter bandwidth

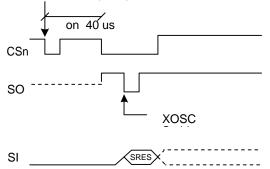

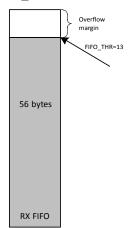

- Data buffering with the 64-byte RX FIFO Packet

radio hardware support

Details of each configuration register can be found in Section 26 starting on page 45.

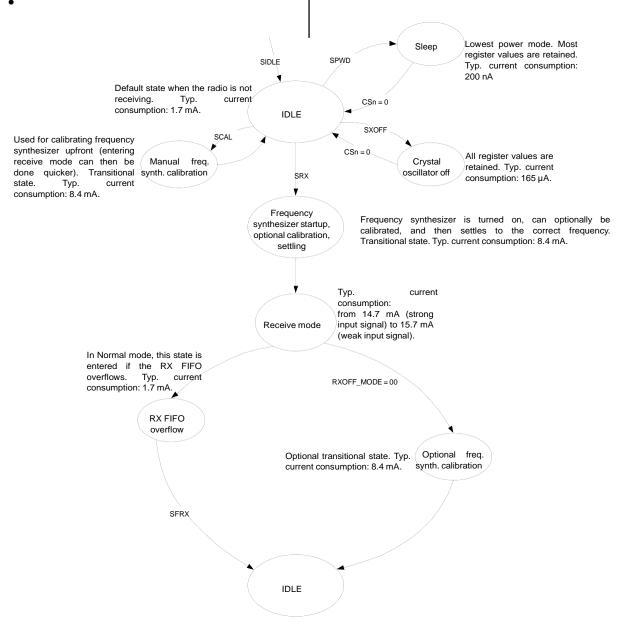

Figure 12 shows a simplified state diagram that explains the main **AKOD4-R** states together with typical usage and current consumption. For detailed information on controlling the **AKOD4-R** state machine, and a complete state diagram, see Section 18, starting on page 35.

Figure 9: Simplified Radio Control State Diagram, with Typical Current Consumption at 1.2 kBaud Data Rate and MDMCFG2.DEM\_DCFILT\_OFF=1 (current optimized). Frequency Band = 868 MHz

**AKOD4-R** can be configured using the SmartRF<sup>™</sup> Studio software [4]. The SmartRF Studio software is highly recommended for obtaining optimum register settings, and for evaluating performance and functionality. After chip reset, all the registers have default values as shown in the tables in Section 26. The optimum register setting might differ from the default value. After a reset all registers that shall be different from the default value therefore needs to be programmed through the SPI interface.

AK004-

DAT

# 10 4-wire Serial Configuration and Data Interface

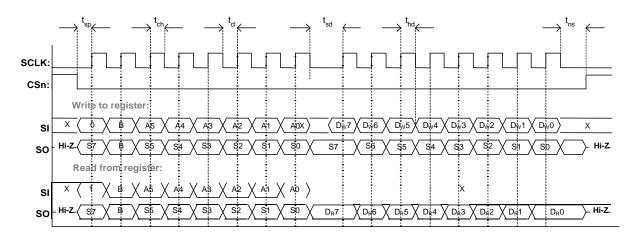

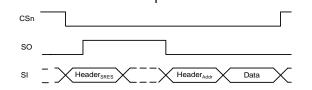

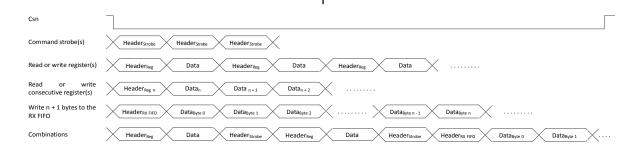

**AK004-R** is configured via a simple 4-wire SPIcompatible interface (SI, SO, SCLK and CSn) where **AK004-R** is the slave. This interface is also used to read buffered data. All transfers on the SPI interface are done most significant bit first.

All transactions on the SPI interface start with a header byte containing a R/W bit, a burst access bit (B), and a 6-bit address ( $A_5 - A_0$ ).

The CSn pin must be kept low during transfers on the SPI bus. If CSn goes high during the transfer of a header byte or during read/write from/to a register, the transfer will be cancelled. The timing for the address and data transfer on the SPI interface is shown in Figure 13 with reference to Table 15.

When CSn is pulled low, the MCU must wait until **AK004-R** SO pin goes low before starting to transfer the header byte. This indicates that the crystal is running. Unless the chip was in the SLEEP or XOFF states, the SO pin will always go low immediately after taking CSn low.

Figure 10: Configuration Registers Write and Read Operations

# Table 14: SPI Interface Timing Requirements

| Parameter          | Description                                                                                                                                                            |               | Min | Max | Units |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|-------|

| f <sub>sclk</sub>  | SCLK frequency<br>100 ns delay inserted between address byte and data byte (single access), or<br>between address and data, and between each data byte (burst access). |               |     | 10  | MHz   |

|                    | SCLK frequency, single access. No delay between address and o                                                                                                          | data byte     | -   | 9   |       |

|                    | SCLK frequency, burst access. No delay between address and data byte, or between data bytes                                                                            |               |     |     |       |

| t <sub>sp,pd</sub> | CSn low to positive edge on SCLK, in power-down mode                                                                                                                   |               | 150 | -   | μs    |

| t <sub>sp</sub>    | CSn low to positive edge on SCLK, in active mode                                                                                                                       |               |     | -   | ns    |

| t <sub>ch</sub>    | Clock high                                                                                                                                                             |               | 50  | -   | ns    |

| t <sub>cl</sub>    | Clock low                                                                                                                                                              |               | 50  | -   | ns    |

| t <sub>rise</sub>  | Clock rise time                                                                                                                                                        |               | -   | 40  | ns    |

| t <sub>fall</sub>  | Clock fall time                                                                                                                                                        |               | -   | 40  | ns    |

| t <sub>sd</sub>    | Setup data (negative SCLK edge) to positive edge on SCLK                                                                                                               | Single access | 55  | -   | ns    |

|                    | $(t_{sd} applies between address and data bytes, and between data bytes)$                                                                                              | Burst access  | 76  | -   |       |

| t <sub>hd</sub>    | Hold data after positive edge on SCLK                                                                                                                                  |               | 20  | -   | ns    |

| t <sub>ns</sub>    | Negative edge on SCLK to CSn high.                                                                                                                                     |               |     | -   | ns    |

**Note:** The minimum  $t_{sp,pd}$  figure in Table 15 can be used in cases where the user does not read the CHIP\_RDYn signal. CSn low to positive edge on SCLK when the chip is woken from power- down depends on the start-up time of the crystal being used. The 150 µs in Table 15 is the crystal oscillator start-up time measured on [1] and [2] using crystal AT-41CD2 from NDK.

# 10.1 Chip Status Byte